# 5ESS<sup>®</sup> Switch Software Analysis Guide

### 5E13 and Later Software Releases

235-600-510 Issue 5.00B June 2001

#### Copyright © 2001 Lucent Technologies. All Rights Reserved.

This electronic information product is protected by the copyright and trade secret laws of the United States and other countries. The complete information product may not be reproduced, distributed, or altered in any fashion. Selected sections may be copied or printed with the utilities provided by the viewer software as set forth in the contract between the copyright owner and the licensee to facilitate use by the licensee, but further distribution of the data is prohibited.

For permission to reproduce or distribute, please contact the Product Development Manager as follows:

1-800-645-6759 (from inside the continental United States)

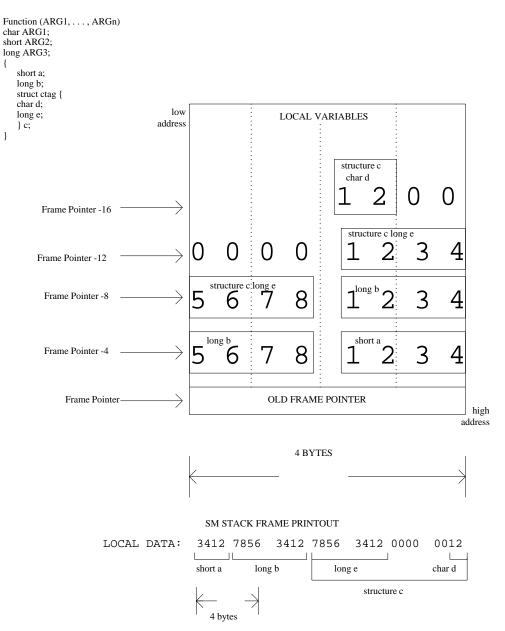

+1-317-322-6847 (from outside the continental United States).

#### Notice

Every effort was made to ensure that the information in this information product was complete and accurate at the time of publication. However, information is subject to change.

This information product describes certain hardware, software, features, and capabilities of Lucent Technologies products. This information product is for information purposes; therefore, caution is advised that this information product may differ from any configuration currently installed.

#### Mandatory Customer Information

Interference Information: Part 15 of FCC Rules - Refer to the 5ESS® Switch Product Specification information product.

#### Trademarks

5ESS is a registered trademark of Lucent Technologies in the United States and other countries AnyMedia is a registered trademark of Lucent Technologies in the United States and other countries Common Language is a registered trademark, and CLEI, CLLI, CLCI, and CLFI are trademarks of Bell Communications Research, Inc. DATAKIT is a registered trademark of Lucent Technologies in the United States and other countries INTEL is a registered trademark of Intel Corporation Motorola is a registered trademark of Motorola, Inc. OneLink Manager is a trademark of Lucent Technologies in the United States and other countries PowerPC is a trademark of International Business Machines Corporation SLC is a registered trademark of Lucent Technologies in the United States and other countries UNIX is a registered trademark of The Open Group in the United States and other countries.

#### Limited Warranty

Warranty information applicable to the 5ESS<sup>®</sup> switch may be obtained from the Lucent Technologies Account Management organization. Customer-modified hardware and/or software is not covered by this warranty.

#### **Ordering Information**

This information product is distributed by the Lucent Technologies Customer Information Center in Indianapolis, Indiana.

The order number for this information product is 235-600-510. To order, call the following:

1-888-LUCENT8 (1-888-582-3688) or fax to 1-800-566-9568 (from inside the continental United States)

+1-317-322-6847 or fax to +1-317-322-6699 (from outside the continental United States).

#### Support Telephone Numbers

Information Product Support Telephone Number: To report errors or ask nontechnical questions about this or other information products produced by Lucent Technologies, call 1-800-645-6759.

*Technical Support Telephone Numbers:* For initial technical assistance, call the North American Regional Technical Assistance Center (NARTAC) at 1-800-225-RTAC (1-800-225-7822). For further assistance, call the Customer Technical Assistance Management (CTAM) center as follows:

1-800-225-4672 (from inside the continental United States)

+1-630-224-4672 (from outside the continental United States).

Both centers are staffed 24 hours a day, 7 days a week.

#### Acknowledgment

Developed by Lucent Technologies Customer Training and Information Products.

# Lucent Technologies values your comments!

## 5ESS<sup>®</sup> Switch Software Analysis Guide 5E13 and Later Software Releases

#### 235-600-510 5.00B June 2001

Lucent Technologies welcomes your comments on this information product. Your opinion is of great value and helps us to improve.

#### 1. Was the information product:

|                                             | Yes | No | Not<br>applicable |

|---------------------------------------------|-----|----|-------------------|

| In the language of your choice?             |     |    |                   |

| In the desired media (paper, CD-ROM, etc.)? |     |    |                   |

| Available when you needed it?               |     |    |                   |

| Please provide any additional comments:     |     |    |                   |

#### 2. Please rate the effectiveness of this information product:

|                         | Excellent | More than satisfactory | Satisfactory | Less than satisfactory | Unsatisfactory | Not<br>applicable |

|-------------------------|-----------|------------------------|--------------|------------------------|----------------|-------------------|

| Ease of use             |           |                        |              |                        |                |                   |

| Level of detail         |           |                        |              |                        |                |                   |

| Readability and clarity |           |                        |              |                        |                |                   |

| Organization            |           |                        |              |                        |                |                   |

| Completeness            |           |                        |              |                        |                |                   |

| Technical accuracy      |           |                        |              |                        |                |                   |

| Quality of translation  |           |                        |              |                        |                |                   |

| Appearance              |           |                        |              |                        |                |                   |

If your response to any of the above questions is "Less than satisfactory" or "Unsatisfactory," please explain your rating.

#### 3. If you could change one thing about this information product, what would it be?

#### 4. Please write any other comments about this information product:

#### Please complete the following if we may contact you for clarification or to address your concerns:

| Name:                 | Date:             |

|-----------------------|-------------------|

| Company/organization: | Telephone number: |

| Address:              |                   |

| Email address:        | Job function:     |

If you choose to complete this form online, go to http://www.lucent-info.com/comments

Otherwise fax to 407 767 2760 (U.S.) or +1 407 767 2760 (outside the U.S.) or email comments to ctiphotline@lucent.com

# Lucent Technologies values your comments!

## 5ESS<sup>®</sup> Switch Software Analysis Guide 5E13 and Later Software Releases

#### 235-600-510 5.00B June 2001

Lucent Technologies welcomes your comments on this information product. Your opinion is of great value and helps us to improve.

#### 1. Was the information product:

|                                             | Yes | No | Not<br>applicable |

|---------------------------------------------|-----|----|-------------------|

| In the language of your choice?             |     |    |                   |

| In the desired media (paper, CD-ROM, etc.)? |     |    |                   |

| Available when you needed it?               |     |    |                   |

| Please provide any additional comments:     |     |    |                   |

#### 2. Please rate the effectiveness of this information product:

|                         | Excellent | More than satisfactory | Satisfactory | Less than satisfactory | Unsatisfactory | Not<br>applicable |

|-------------------------|-----------|------------------------|--------------|------------------------|----------------|-------------------|

| Ease of use             |           |                        |              |                        |                |                   |

| Level of detail         |           |                        |              |                        |                |                   |

| Readability and clarity |           |                        |              |                        |                |                   |

| Organization            |           |                        |              |                        |                |                   |

| Completeness            |           |                        |              |                        |                |                   |

| Technical accuracy      |           |                        |              |                        |                |                   |

| Quality of translation  |           |                        |              |                        |                |                   |

| Appearance              |           |                        |              |                        |                |                   |

If your response to any of the above questions is "Less than satisfactory" or "Unsatisfactory," please explain your rating.

#### 3. If you could change one thing about this information product, what would it be?

#### 4. Please write any other comments about this information product:

#### Please complete the following if we may contact you for clarification or to address your concerns:

| Name:                 | Date:             |

|-----------------------|-------------------|

| Company/organization: | Telephone number: |

| Address:              |                   |

| Email address:        | Job function:     |

If you choose to complete this form online, go to http://www.lucent-info.com/comments

Otherwise fax to 407 767 2760 (U.S.) or +1 407 767 2760 (outside the U.S.) or email comments to ctiphotline@lucent.com

#### Software Analysis Guide

#### CONTENTS PAGE 1. 1-1 2. 2-1 C PROGRAMMING LANGUAGE 3. 3-1 4-1 4. 5. 5-1 GENERIC ACCESS PACKAGE (GRASP)/ENHANCED GRASP. . . . . 6. 6-1 7. GENERIC UTILITIES. 7-1 8. 8-1 9. 9-1 10-1 11. 11-1 12-1 13-1 A1. ENVIRONMENT TO PATHNAME CROSS REFERENCE . . . . . . . . A1-1 A2. IS25, 3B20, AND 3B21 COMPUTER INSTRUCTION LIST (BY A2-1 A3. Motorola MC68000 PROCESSOR FAMILY INSTRUCTION SET . . . . A3-1 A4. Intel 8086 AND 80186 PROCESSOR INSTRUCTION SET. A4-1 A5. PowerPC PROCESSOR FAMILY INSTRUCTION LIST (BY A5-1 A6. SWITCHING MODULE ASSERT ANALYSIS EXAMPLE AUDIT A6-1 G-1 I-1

### Software Analysis Guide

#### CONTENTS

#### PAGE

| 1. | INTRO |                                   | 1-1 |

|----|-------|-----------------------------------|-----|

|    | 1.1   | PURPOSE                           | 1-1 |

|    | 1.2   |                                   | 1-1 |

|    |       | 1.2.1 General                     | 1-1 |

|    |       | 1.2.2 Supported Software Releases | 1-1 |

|    |       | 1.2.3 Terminology                 | 1-1 |

|    | 1.3   | ORGANIZATION                      | 1-3 |

|    | 1.4   | USER FEEDBACK                     | 1-4 |

|    | 1.5   | DISTRIBUTION                      | 1-5 |

|    | 1.6   |                                   | 1-5 |

|    | 1.7   | REFERENCES                        | 1-5 |

#### 1. INTRODUCTION

#### 1.1 PURPOSE

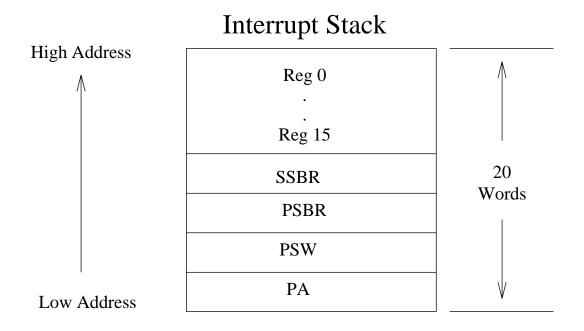

This document contains information and directions for using tools to analyze software-related problems within the  $5ESS^{(B)}$  switch. It deals with administrative module (AM), communications module (CM) and switching module (SM) software problems, such as asserts, audits and interrupts, as well as program language usage and program code documentation.

The content assumes the user can read and understand assembly and C programming languages pertaining to the *5ESS* switch. The *Software Analysis Guide* should be used as a problem solving tool. Each component can be used independently to research or investigate a point of interest, or the document can be read from beginning to end as one might read a book. The intention is to facilitate the identification and resolution of problems within the *5ESS* switch.

Use of this guide will help the user become familiar with the structure and content of the program code, the organization, and use of error messages as well as understand the interactive languages which permit the human interface with the switch.

#### **1.2 UPDATE INFORMATION**

#### 1.2.1 General

As the *5ESS* switch evolves with new capabilities and features, this document will be updated. This issue includes an updated procedure for accessing the online program listings, Section 2.2.

#### 1.2.2 Supported Software Releases

In accordance with the 5ESS Switch Software Support Plan, the 5E12 software release is rated Discontinued Availability (DA) as of September, 2000. The information supporting 5E12 and earlier is being removed over time, instead of concurrently, from all documentation.

If you are supporting offices that use a software release prior to 5E13 and you have a need for the information that is being removed, retain the associated pages as they are removed from the paper documents, or retain the earlier copy of the CD-ROM.

#### 1.2.3 Terminology

#### 1.2.3.1 Lucent Electronic Delivery

The Lucent Electronic Delivery system is replacing the Software Change Administration and Notification System (SCANS) as the system used to download software changes to Lucent products. During the transition, both systems will be supported. When products no longer require SCANS, Lucent Technologies will notify any customers still using SCANS of the plans for completing the migration to Lucent Electronic Delivery. The **OneLink Manager**<sup>TM</sup> ASM User's Guide, 235-200-145, describes the Lucent Electronic Delivery system. Documentation currently referencing SCANS will be changed over time, as other technical changes are required.

#### 1.2.3.2 Communication Module Name Change

The term Communication Module (CM) has been changed to the Global Messaging Server (GMS), representing the new portfolio name of this particular module. The current names of the specific types of the GMS (the CM2 and CM3) have not been changed. Where the CM name has been used in a generic way within this information product, the name will be changed to GMS. Where the specific version of GMS (CM2 or CM3) is being described or mentioned, the name will not be changed. However, the GMS name may be added to the description in certain places as a reminder of the change, and that the particular version is a part of the overall portfolio. The following list provides some examples of how you may see these names used together:

- Global Messaging Server (formerly Communication Module)

- GMS (formerly CM) Global Messaging Server-CM2

- GMS-CM2

- Global Messaging Server-CM3

- GMS-CM3.

These name changes will be made over time as other technical changes are required. Also these changes may not be reflected in all software interfaces (input and output messages, master control center screens, and recent change and verify screens). Where the information product references these areas, the names are used as they are within the software interface.

#### 1.2.3.3 Bellcore/Telcordia Name Change

As of March 18, 1999, Bellcore officially changed its name to Telcordia Technologies. Not all pages of this document are being reissued to reflect this change; instead, the pages will be reissued over time, as technical and other changes are required. Customers on standing order for this document may see that, on previous-issue pages, the Bellcore name is still exclusively used.

Customers receiving new orders for this document will see the Telcordia Technologies name used as appropriate throughout the document, and the Bellcore name used only to identify items that were produced under the Bellcore name. Exceptions may exist in software-influenced elements such as input/output messages, master control center screens, and recent change/verify screens. These elements will not be changed in this document until such time as they are changed in the software code. Document updates will not be made specifically to remove historical references to Bellcore.

#### 1.2.3.4 5ESS-2000 Switch Name Change

This 5ESS switch document may contain references to the 5ESS switch, the 5ESS-2000 switch, and the 5ESS  $AnyMedia^{\mbox{\sc s}}$  Switch. The official name of the product has been changed back to the 5ESS switch. In the interim, assume that any reference to the 5ESS-2000 switch or the 5ESS AnyMedia Switch is also applicable to the 5ESS switch. It should be noted that this name change may not have been carried forward into software-influenced items such as input and output messages, master control center screens, and recent change/verify screens.

#### 1.2.3.5 National ISDN

National ISDN is an evolving platform in which new features will continue to be introduced for new revenue opportunities, improved operational efficiencies, and for support of specific applications. NI 1, NI 2, and NI 3 represent specific features as documented in Bellcore SRs 1937, 2120, and 2457. The industry is migrating to an additional terminology to more specifically denote the availability of National ISDN features: NI 95, NI 96, etc. A feature is included in a specific version (such as, NI 96) if it is available by the switch vendors by the first quarter of the year.

#### 1.3 ORGANIZATION

The content and organization of the *Software Analysis Guide* is as follows:

#### • Introduction

Section 1 describes the content and organization of this document. It also describes the reasons for updates and how to obtain assistance.

#### • Using the Program Listings

Section 2 explains the structure and use of on-line program listings.

#### • C Programming Language

Section 3 reviews the C programming language and its use in the 5ESS switch.

#### • Disassembly/Assembly Language

Section 4 reviews the disassembly/assembly language for the 3B20D and 3B21D computers,  $MOTOROLA^{1}$  MC68000 microprocessor family, and the  $Intel^{2}$  80186 microprocessor and discusses their use in the *5ESS* switch.

#### • Assert Analysis

Section 5 explains the function of asserts, the key parts of the printout associated with them, and how to analyze them.

#### Generic Access Package (GRASP)/Enhanced Generic Access Package (EGRASP)

Section 6 discusses the use of the interactive language used in the AM.

#### Generic Utilities

Section 7 explains the use of the interactive language used in the SMs, the CM, and the peripherals.

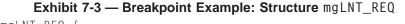

#### • Interrupt Analysis

Section 8 examines the function of an interrupt and discusses the output sent to the receive only printer (ROP).

#### • Single Process Purge Analysis

Section 9 analyzes the function of a single process purge (SPP) and discusses the output received on the ROP.

#### • Audit Analysis

Section 10 discusses audits and the messages received on the ROP.

#### • Data Collection and Analysis

Section 11 discusses the types of data and the manner of data collection necessary to analyze a trouble event so that a complete picture is compiled, particularly an event history.

OSDS Monitor

<sup>1.</sup> Registered trademark of Motorola Inc.

<sup>2.</sup> Registered trademark of Intel Corporation.

Section 12 explains how the operating system for distributed switching (OSDS) monitor tool is used for gathering performance data and investigating performance problems.

#### OSDS Overload Monitor

Section 13 explains how the OSDS overload monitor tool is used for investigating OSDS resource overload problems.

#### • Supplementary Information

The supplementary sections contain various reference materials, including:

#### • Appendix 1: Environment to Pathname Cross Reference

Appendix A1 is provided for use with upd:ftrc to find a failing function.

• Appendix 2: IS25, 3B20D, 3B21D Computer Instruction Set

Appendix A2 is a list of the IS25, 3B20D, and 3B21D Computer opcodes and their functions.

#### • Appendix 3: MOTOROLA MC68XXX Microprocessor Family Instruction Set

Appendix A3 is a list of the MOTOROLA MC68XXX microprocessor family opcodes and their functions.

• Appendix 4: Intel 8086 and 80186 Processor Instruction Set

Appendix A4 is a list of the Intel 8086 and 80186 processor opcodes and their functions.

• Appendix 5: PowerPC<sup>3</sup> Processor Family Instruction List (By Mnemonic)

Appendix A5 includes an instruction field summary, a list of split-field notation and conventions, and the entire *PowerPC* instruction set sorted by mnemonic.

#### • Appendix 6: SM Assert Analysis Example Audit Trail

Appendix A6 is the contents of the header files needed to construct the data organization for the Assert Analysis Example - SM, Section 5.2.2.

• Glossary

The Glossary defines terms and expands acronyms used in this document.

#### 1.4 USER FEEDBACK

We are constantly striving to improve the quality and usability of this information product. Please use one of the following options to provide us with your comments:

- You may use the on-line comment form at http://www.lucent-info.com/comments

- You may email your comments to ctiphotline@lucent.com

- You may print the comment form (located at the beginning of this information product after the Legal Notice) to send us your comments either by fax or mail as follows:

- Fax to **1-407-767-2760**

- Mail to the following address:

<sup>3.</sup> Trademark of International Business Machines Corporation.

Lucent Technologies Documentation Services Coordinator 240 E. Central Parkway Altamonte Springs, FL 32701-9928

• You may call the hot line with your comments. The telephone number is **1-800-645-6759**. The hot line is staffed Monday through Friday from 8:00 a.m. to 5:00 p.m. Eastern time.

Please include with your comments the title, ordering number, issue number, and issue date of the information product, your complete mailing address, and your telephone number.

If you have questions or comments about the distribution of our information products, see Section 1.5, Distribution.

#### 1.5 DISTRIBUTION

For distribution comments or questions, either contact your local Lucent Technologies Account Representative or send them directly to the Lucent Technologies Customer Information Center (CIC) in Indianapolis, Indiana.

A documentation coordinator has authorization from Lucent Technologies to purchase our information products at discounted prices. To find out whether your company has this authorization through a documentation coordinator, call **1-888-LUCENT8** (1-888-582-3688).

Customers who are not represented by a documentation coordinator and employees of Lucent Technologies should order 5ESS switch information products directly from CIC.

To order, call the following telephone number:

- **1-888-LUCENT8 (1-888-582-3688)** or fax to **1-800-566-9568** (from inside the continental United States)

- +1-317-322-6847 or fax to +1-317-322-6699 (from outside the continental United States).

#### 1.6 TECHNICAL ASSISTANCE

For initial technical assistance, call the North American Regional Technical Assistance Center (NARTAC) at **1-800-225-RTAC (1-800-225-7822)**.

For further assistance, call the Customer Technical Assistance Management (CTAM) center at the following number:

- **1-800-225-4672** (from inside the continental United States)

- +1-630-224-4672 (from outside the continental United States).

Both centers are staffed 24 hours a day, 7 days a week.

#### 1.7 REFERENCES

More information is found in the following Lucent Technologies documents:

- 235-105-110 System Maintenance Requirements and Tools

- 235-105-210 Routine Operations and Maintenance Procedures

- 235-105-220 Corrective Maintenance Procedures

- 235-600-400 Audits Manual

- 235-600-500 Asserts Manual

- 235-600-700 Input Messages Manual

- 235-600-750 Output Messages Manual

**Note:** An "x" or "x"s in the last three positions of a release specific document number indicate the digits that change from release to release. Refer to 235-001-001, *Documentation Description and Ordering Guide* for the document number associated with each software release.

### Software Analysis Guide

#### CONTENTS

#### PAGE

| 2.  | USING    | g the pr | ROGRAM L    | ISTINGS   |        |      |      |             |     |    |   |   |   |   |   |   | 2-1 |

|-----|----------|----------|-------------|-----------|--------|------|------|-------------|-----|----|---|---|---|---|---|---|-----|

|     | 2.1      | INTROD   | UCTION TO   | ONLIN     | E PRC  | GR/  | AM L | .IST        | ING | S. |   |   |   |   |   |   | 2-1 |

|     | 2.2      | ONLINE   | ACCESS F    | PROCED    | URE .  |      |      |             |     |    |   |   |   |   |   |   | 2-1 |

|     | 2.3      | THE LIS  | TINGS ME    | NU        |        |      |      |             |     |    |   |   |   |   |   |   | 2-2 |

|     | 2.4      | THE LIS  | TINGS ME    | NU        |        |      |      |             |     |    |   |   |   |   |   |   | 2-2 |

|     | 2.5      | LISTING  | S MENU O    | PTIONS    |        |      |      |             |     |    |   |   |   |   |   |   | 2-3 |

|     | 2.6      | EXAMPL   | _E — USIN   | G THE P   | ROGR   | RAM  | LIST | <b>FING</b> | S.  |    |   |   |   |   |   |   | 2-4 |

|     |          | 2.6.1    | Example I   | ntroduct  | tion . |      |      |             |     |    |   |   |   |   |   |   | 2-4 |

|     |          | 2.6.2    | Determine   | the Fur   | nction | Nam  | ne.  |             |     |    |   |   |   |   |   |   | 2-5 |

|     |          | 2.6.3    | Locate the  | e Functio | on.    | • •  | • •  | •           |     | ·  | · | • | • | • | • | • | 2-6 |

| LIS | ST OF    | EXHIB    | ITS         |           |        |      |      |             |     |    |   |   |   |   |   |   |     |

| Exl | hibit 2- | 1 — AM . | Assert Prir | itout .   |        |      |      |             |     |    |   | • |   |   |   |   | 2-4 |

| Exl | nibit 2- | 2 — Brea | akpoint Lis | ting for  | Functi | on I | Npt  | com         | p() |    |   | • |   |   | • |   | 2-7 |

| Exl | hibit 2- | 3 — Disa | issembly L  | isting fo | r Func | tion | INp  | otco        | mp( | )  |   |   |   |   |   |   | 2-8 |

#### 2. USING THE PROGRAM LISTINGS

#### 2.1 INTRODUCTION TO ONLINE PROGRAM LISTINGS

Program listings consist of C language source code, its corresponding assembly code, and a set of indices for locating code. Online listings are available through a processor at Lucent Technologies, and can be accessed by using the dial-up service provided by Lucent Technologies Web and Media Management (WMM).

Web and Media Management contains various documentation products, including this document and the  $5ESS^{$ ® switch program listings and source code.

Understanding the organization and use of online program listings is fundamental to the process of analyzing and resolving problems in the *5ESS* switch. This section of the Software Analysis Guide describes the organization of the online listings. The listings support the CNI, RTR, and most of the modular subsystems.

Upon completion of this section, the user should be able to locate the desired documentation in the online listings.

*Note:* Users have access to the officially sanctioned *5ESS* switch source files. These files are updated periodically to reflect changes made by the software update mechanism. A message of the day (MOTD) is displayed each time the user accesses the online listings environment. Because the MOTD provides information on the status of the online listings environment (such as stable, unstable, etc.), it is important that users read the MOTD at the start of each login session.

#### 2.2 ONLINE ACCESS PROCEDURE

Use the following procedure to access the online listings.

1. If using a modem, dial 1-630-224-6640 to reach the Lucent Technologies Web and Media Management (WMM) *5ESS* Switch Online Switch Program Listings.

Lucent employees can access the Listing environment via a telnet session to 135.185.130.28.

- 2. The system will prompt you to: Enter your login and password. (If you do not have a login and password you should contact 1-888-LUCENT-8. Lucent employees should call 1-800-228-6763.)

- 3. From the Lucent Technologies Document Menu, select *5ESS* Switch Program Listings.

- 4. From the next menu, *5ESS* Switch Listings Program select ...... Execute Listings.

- a. The following instructions are displayed:

Remember "exit" or "CTRL-D" will take you back to IDS ENTER "LIST" It Will Put You Into The LISTING Menu Please remove your files when you are finished. ENTER RETURN TO CONTINUE...

- b. Press <Return>.

- 5. The Listings Environment menu is displayed; select the desired software release. After the message "Now entering the 5EX(x) and later listings environment," a submenu is presented; again, specify the desired software release.

Enter your choice from the menu and press <return>.

The following message is displayed:

Enter editor desired (less or more) Enter desired choice (less or more) and <return>.

a. The system will then reply:

```

THE ENVIRONMENT SETUP COMPLETE FOR LISTINGS.

Enter RETURN to CONTINUE

```

b. You will then be prompted to make a choice of setting up your environment to use Stackmap and Other Tools. Make your selection. To select Stackmap simply type in y (yes) at the prompt.

The system will then prompt you to select a subsystem from the list that is displayed on the screen.

#### 2.3 THE LISTINGS MENU

The Listings Menu provides options for accessing the online program listings. It uses several environment variables that were set when the "Execute Listings" option was selected.

The menu display looks like:

```

5EX(X)XX.XX (SU LEVEL XX-XXXX) LISTINGS MENU

1) SYMBOL/FUNCTION DEFINITION

2) SOURCE FILE NAME

3) SYMBOL/FUNCTION REFERENCES

4) RTR NAMELIST

5) DGN SOURCE CODE CROSS-REFERENCE

6) POPRULES FILE

7) GENERATE BREAKPOINT/DISASSEMBLY LISTINGS

8) CDB INTERACTIVE MENU (FOR EXPERIENCED USERS)

9) EXIT

```

Enter Choice (RETURN will exit)-=>

To use this menu and its options,

- When prompted for a selection, type its associated number followed by <Return>.

- When prompted for a name, type the name of the product followed by <Return>.

- Press <Return> to display the previous screen. Entering <Return> from the Listings Menu will exit the program.

#### 2.4 THE LISTINGS MENU

The Listings Menu provides options for accessing the online program listings. It uses several environment variables that were set when the "Execute Listings" option was selected.

The menu display looks like:

5EX(X)XX.XX (SU LEVEL XX-XXXX) LISTINGS MENU

1) SYMBOL/FUNCTION DEFINITION

2) SOURCE FILE NAME

3) SYMBOL/FUNCTION REFERENCES

4) RTR NAMELIST

5) DGN SOURCE CODE CROSS-REFERENCE

6) POPRULES FILE

7) GENERATE BREAKPOINT/DISASSEMBLY LISTINGS

8) CDB INTERACTIVE MENU (FOR EXPERIENCED USERS)

9) EXIT

#### Enter Choice (RETURN will exit)-=>

To use this menu and its options,

- When prompted for a selection, type its associated number followed by <Return>.

- When prompted for a name, type the name of the product followed by <Return>.

- Press <Return> to display the previous screen. Entering <Return> from the Listings Menu will exit the program.

#### 2.5 LISTINGS MENU OPTIONS

Several menu options display a list of valid processor types and prompt the user to choose from the list. Select ASM to specify the traditional switching module (SM), and ASM2K to specify the SM-2000.

A brief description of each menu item follows.

• Symbol/Function Definition

This option prompts for a symbol name. This can be a function, macro, or C variable defined as an extern (that is, a global variable).

If the symbol or function is found, the system prompts the user to select from a list of path names to read the appropriate file.

• Source File Name

This option prompts for a file name. If the specified file is located, the system displays a list of file locations and prompts the user to select one for viewing.

• Symbol/Function References

This option prompts for a symbol name. This can be a function, macro, or C variable defined as an extern (that is, a global variable).

If the symbol is found, the system prompts the user to select from a list of path names.

• RTR Namelist

This option provides symbol and address information for the RTR environment. It can also be used to list the RTR Namelist files.

• DGN Source Code Cross-Reference

This option provides a way to identify the function associated with a specific hardware diagnostic phase.

This option initiates a series of interactive sub-menus. For *5ESS* switch application hardware, the path name to the diagnostic source code is provided. For RTR diagnostics (such as CU, MHD, etc.) the path name to the breakpoint file is given.

• Population Rules File

The Automated Static Office Dependent Data (SODD) Audit is a feature that uses the source files of Population Rule Language, Version 5.0 (PRL 5.0) to

perform integrity checks on the office dependent data. Use this option to examine the checks section of the PRL 5.0 source code when analyzing SODD audit errors. At the prompt:

```

Please enter Poprule File -=>

```

enter the name of a relation, in lower case, preceded by RL, and appended with a . R. For example, enter RLfc\_line.R to display the population rules for relation FC\_LINE.

The online PRL 5.0 source code files include the latest software updates to the population rules.

• Generate Breakpoint/Disassembly Listings

This option prompts the user for additional input, via a sub-menu. The sub-menu enables the user to generate either a breakpoint or disassembly listing, or both. The user is prompted for the subsystem name and the subsystem module name, information that is part of the path name information output in response to a function name query from the Symbol/Function Definition of the Listings Menu. Note that the online listings environment does not support the creation of CNI breakpoint or disassembly listings.

```

//XS845/inteam1z/si_app/5e11_1z/si/INcmpict1/INrecovery.c

subsystem

name

subsystem

module

name

```

• CDB Interactive Menu (For Experienced Users)

Use this option to gain access to the CDB tool. For information about its use, please refer to Item 5 (CDB1 - Manual Pages) under the *5ESS* Switch On-Line Field Grade LISTINGS sub-menu.

• Exit

Use this option to exit the Listings Menu.

#### 2.6 EXAMPLE — USING THE PROGRAM LISTINGS

#### 2.6.1 Example Introduction

This section presents an example of how one might use the online program listings to locate and analyze the source code associated with a failing function. While it is beyond the scope of this example to detail all aspects of assert analysis, it does provide an explanation of the steps needed to locate the source code associated with a specific function. See "Assert Analysis," Section 5 for more detail.

Assert messages contain a failing address, one or more stack trace addresses and, as in the case of this AM example, the environment in which the assert fired. This information will be used to identify the failing function. See Exhibit 2-1 for a sample of the AM Assert printout.

#### Exhibit 2-1 — AM Assert Printout

```

S570-262181 88-09-28 06:03:55 000640

INIT AM LVL=RPI FPUMP DEF-CHK-FAIL= 1275 EVENT=373 COMPLETED

SW-ERR FAIL-ADDR=H'19b2 AM-MODE NORMAL CU 1 TIME 3:52:3

PROCESS: OSDS=0,0 CALL-INTJ NONE DMERT 262254 EVENT-FLAGS=0'0

FCODE=0

```

| REQ-PROC O HI                                                | DW-LVL O                                                                                                                       | SPP-COU                                                                                                                   | NTS=0,0                                                                                                                   | NO-AUD-SCH                                                                                                                      | ED                                                                                                                             |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| S570-262181 88<br>REPT AM STACK<br>USER: 00001<br>00000      | TRACE ENV<br>9b2 00000                                                                                                         | =FPUMP SRC<br>C14 00002                                                                                                   | =DCF EVENT                                                                                                                |                                                                                                                                 | 6F8 0000D66                                                                                                                    |

| S570-262181 88<br>REPT AM STACL<br>FUNC ADDR:<br>PARAMETERS: | -09-28 06:<br>K FRAME EN<br>H'19b2<br>000004FB<br>00000000                                                                     |                                                                                                                           | 42<br>RC DCF EVE<br>00040160<br>00200000                                                                                  | NT=373<br>00040190<br>0000001                                                                                                   | 00040190                                                                                                                       |

| LOCAL DATA:                                                  | 000004FB<br>00060014<br>00200000<br>000401D4<br>003CC70B                                                                       | 00001A26<br>010002A6<br>00000001<br>00040208<br>00040100                                                                  | 00040190<br>00000001<br>20000000<br>00000454<br>00040200                                                                  | 000401D4<br>00000000<br>00000000<br>00000002<br>00001A26                                                                        | 00000001<br>00040000<br>00040200<br>04FB0000<br>000401D4                                                                       |

|                                                              | 00040200<br>00040208<br>00040240<br>00000000                                                                                   | 00040214<br>00040240<br>00000001<br>00000000                                                                              | 000022C2<br>00000000<br>00000000<br>00000000<br>00000000                                                                  | 000401D4<br>000000FA<br>00040000<br>00000000                                                                                    | 00040200<br>00040208<br>00200000<br>00000000                                                                                   |

| S570-262181 88<br>REPT AM STAC<br>FUNC ADDR:                 | -09-28 06:<br>K FRAME EN<br>H'c14                                                                                              |                                                                                                                           | 43<br>RC DCF EVE                                                                                                          | NT=373                                                                                                                          |                                                                                                                                |

| PARAMETERS:<br>LOCAL DATA:                                   | 00040110<br>00040000<br>000004FB<br>0000000<br>00040000<br>00001A26<br>010002A6<br>0000001<br>00040208<br>00040100<br>00040000 | 4000000<br>0020000<br>00000014<br>004000<br>00200000<br>0004019C<br>00000001<br>2000000<br>0000454<br>0004020C<br>0000000 | 00002844<br>0000001<br>0020000<br>0000001<br>000401D4<br>0000000<br>0000000<br>0000000<br>00000002<br>00001A26<br>0000000 | 000400D4<br>0000001<br>00040190<br>00000001<br>40000000<br>00040000<br>00040000<br>00040200<br>04FB0000<br>000401D4<br>00000000 | 00040110<br>0000000<br>00040190<br>0000000<br>000004FB<br>00060014<br>00200000<br>000401D4<br>003CC70E<br>0004020C<br>0004020C |

Note the failing address and environment in the printout and use this information to generate breakpoint and disassembly listings for the failing function.

- Failing address 0x000019b2

- Environment FPUMP

#### 2.6.2 Determine the Function Name

The first step is to identify the path name of the environment. Use "Environment to Pathname Cross Reference," Appendix A1 to accomplish this step. Next, the upd:ftrc input message is used to identify the failing function:

upd:ftrc:fn="/no5text/prc/fpump",addr=h'19b2;

The format of the upd:ftrc output is:

| UPD FTRC REPT     |           |                    |             |    |             |        |       |

|-------------------|-----------|--------------------|-------------|----|-------------|--------|-------|

| OBJECT_FILE=/no5t | ext/prc/f | <sup>-</sup> pump_ | 0 F F 6 F T |    | <b>FT F</b> | C)//// |       |

| ADDRESS FUNCTION  | START     | SIZE               | OFFSEI      | IV | FILE        | SYM    | INDEX |

| 19b2 INptcomp     | 18dc      | 138                | d6          | 16 | INfpump_c.c | [      | 32]   |

The offset into the function is calculated by the switch and is included in the UPD FTRC REPT output message. The offset is needed so that the user will know the exact point of failure in the function.

#### 2.6.3 Locate the Function

Use the "On-Line Access Procedure," Section 2.2 to access Web and Media Management and examine the source code.

Select option 1 (SYMBOL/FUNCTION DEFINITION) and, when prompted, enter the name of the failing function  ${\tt INptcomp}.$

When prompted, select from the list of valid processor types. Choosing the default (<Return>) will cause the data tables for *all* processor types to be searched, significantly increasing the search time. For a more efficient search specify the processor type when known. In this example, AM was specified. The system will now display the name of the file that contains the failing function.

Note the relative path of the source file, in particular the subsystem and subsystem module names. This information will be needed to generate breakpoint and/or disassembly listings. View the file to verify that it contains the function definition.

In this example, the relative path is .../si/INampump/INfastpump.c. The function exists in subsystem si, subsystem module INampump. Note that the subsystem and subsystem module names are case sensitive; this becomes important when breakpoint or disassembly listings are to be created.

Return to the main Listings menu by pressing <Return>, then select option 7 (GENERATE BREAKPOINT/DISASSEMBLY LISTINGS).

When prompted, specify the type of listings to generate. For this example, both breakpoint and disassembly listings are requested.

Next, enter a processor type. Since there is no default on this menu, a valid processor type must be specified.

Enter the subsystem and, when prompted, the subsystem module name. Recall that these names are case sensitive and must be entered exactly as displayed by the SYMBOL/FUNCTION DEFINITION search.

The system now displays a list of the files that were generated for the specified subsystem. Depending on the subsystem module, several module product files may have been created. Select the disassembly file for the module product desired. In this example, the file of interest is .../INfpump.dis.

Use standard vi commands to search the file for the function name; in this instance, the function is INptcomp(). (See Exhibit 2-3.)

Once the start of the function has been located, take note of the relative start address. The relative start address of this function is h'1948. To determine the exact point at which the assert fired, the previously calculated offset (h'd6) must be added to this start address: h'1948 + h'd6 = h'1a1e. Thus, h'1a1e marks the relative address of the instruction immediately following the assert macro call (though this doesn't ALWAYS hold true).

An examination of the assembly code reveals that the failure occurred in the instruction set associated with breakpoint [37]. The next step is to locate this breakpoint line in the breakpoint listing for function INptcomp() and determine the reason for the assert. (See Exhibit 2-2).

Quit the disassembly file, INfpump.dis, and the list of generated files for the subsystem module will be displayed again.

Select the breakpoint file for the module product desired. For this example, the file is .../INfpump.bp.

Search the file for the definition of the function INptcomp(). Since this file contains code for numerous functions, the first occurrence of function INptcomp() may not be its definition, but rather a call to it from another function. Use standard vi commands to step beyond these references. Note that the full name of the desired function is INptcompmsg(); by convention, only the first eight characters of a function name are used for software releases prior to 5E11(1). As of the 5E11(1) software release, C function/variable names can be longer than eight characters. The INptcomp() example is still valid in the 5E11(1) online listing environment; however, the upd:ftrc output would have listed the function's name as INptcompmsg() and all references to the eight-character name in the example would be replaced with the full function name.

Once the source code of the failing function has been located, search for the desired breakpoint line. In this example the breakpoint line is [37]. The C-language source code can now be analyzed to determine why the assert fired.

Repeat this procedure to locate variables or functions referenced by function INptcomp().

```

AM: INFPUMP

@FUNCTION: INptcomp (INfpump_c.o)

/*

* Function:

INptcompmsq()

*

This function will format and send the PARTIALLY COMPLETE

Description:

message to the SM and then clear the control structure that

the information was taken out of.

*

*

Parameters:

None.

*

*

None

Returns:

*

*

Calls:

INeventno()

- get an event number

- format OSDS message

INfosmsg()

*

INperror()

- pump error handler

*

sendport()

- send a message

*

Externals:

INpartinfo[]

- section start addresses for sections pumped

- FPUMP message buffer

msgbuf

*

- FPUMP misc. information area

ctrl

*/

void

INptcompmsg()

{

INBCASTMSG

bcastmsg;

/* message to broadcast pump */

/* pointer to control structure */

/* useful_index */

INCNTRITBI

*partinfo_ptr;

i;

unsigned short

partinfo_ptr = &INpartinfo[INcurrent

^ 1];

[6]

[8]

if ( INlinkname == 0 ) {

[9]

msgbuf.btmsg.osds_hdr.realhdr.type &= ~LINKMASK;

}else{

msgbuf.btmsg.osds_hdr.realhdr.type |= LINKMASK;

[11]

INlinkname ^= 1;

[13]

/* send the message provided that this is NOT an offline pump */

if ( ! INISOFFLINEPUMP( ctrl.ptype ) ) {

/* Fill in the header that the SMs will see. */

[16]

bcastmsg.msghead.type = MGPUFPMP

[18]

[19]

bcastmsg.msghead.priority = INMSGPRIOR;

```

Exhibit 2-2 — Breakpoint Listing for Function INptcomp()

[20] bcastmsg.msghead.length = sizeof( struct mgPUFPMP ); /\* Fill in the body that the SMs will see. \*/ [23] [24] bcastmsg.msgs.pufpmp.ccode = INPARTSUCC; bcastmsg.msgs.pufpmp.nblocks = partinfo\_ptr->no\_blocks; bcastmsg.msgs.pufpmp.lastbyte = partinfo\_ptr->lstbytpmp; Ī25Ī AP# 88/INptcomp /INptcomp FPUMP Handling Process Control Functions 5ESS AM:INFPUMP ISSUE 01 PAGE 88 SEE PROPRIETARY NOTICE ON COVER PAGE PR-5D12010-71 AM: INFPUMP [26] [29] F307 r[i]; [31] /\* store total number of sections in the message \*/ bcastmsg.msgs.pufpmp.strtaddr[0] = (unsigned long)partinfo\_ptr->tot [33] \_sect; /\* Broadcast the Partial Complete message to the SMs. \*/ [36] if (INfhbcastsend(&bcastmsg,ctrl.pumping\_sms,ctrl.bootpid.procno)!= SUCCESS) { [37] INperror( INPUSDPT ); } /\* clear the control structure that was just used \*/ [43] partinfo\_ptr->lstbytpmp = OL; Ī44Ī partinfo\_ptr\$>no\_blocks = 0; [45] partinfo\_ptr->tot\_sect = 0; /\* Indicate that we are making progress for fast pump \*/

if (( ctrl.ptype == INFP ) || ( ctrl.ptype == INBCP )) {

SIpprog[ INFP ].event\_no = INeventno(); [48] Ī49Ī /\* save the time that progress is updated \*/

INprog\_time = getime(); [52] } [54] } AP# 89/INptcomp /INptcomp FPUMP Handling Process Control Functions 5ESS AM:INFPUMP ISSUE 01 PAGE 89 PR-5D12010-71 SEE PROPRIETARY NOTICE ON COVER PAGE 11/ 6/91 Exhibit 2-3 — Disassembly Listing for Function INptcomp() AM: INFPUMP @DISASSEMBLY: INptcomp (INfpump\_c.o) \*\*\*\* 3b DISASSEMBLER \*\*\*\* disassembly for INfpump c.o section .text INptcomp() 1948: 7a20 &0x2,&0x0 save 194a: 346a 06cb 194e: 4448 0004 1f80 1954: 3221 0000 &0x6c,%sp \$0x41f8,%r0 addw2 [6] movzbw

xorw2

&0x1,%r0

| [8]<br>[9]<br>[11]<br>[13]<br>[16]<br>[18]<br>[19]<br>[20]<br>[23]<br>[24]<br>[25]<br>[26]<br>[29]<br>[30] | 1958:       34         1956:       34         1964:       14         1966:       20         1978:       80         1978:       20         1978:       20         1978:       20         1978:       20         1978:       20         1978:       20         1978:       20         1998:       22         1998:       22         1998:       22         1998:       22         1998:       23         1998:       24         1900:       40         1904:       44         19b6:       14         19b8:       55         19b8:       55         19b8:       55         19b8:       55         19b8:       55         19c6:       40         19c6:       42         19c6:       42         19c4:       55         19d8:       69         19d8:       69         19c4:       55         19c4:       55 | 408         016         016         100         100         100         100         100         100         100         101         100         101         100         101         102         103         104         105         106         107         108         109         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         101         102         103         101         102         103         104         105         105         106         107         108         108         109         101         1 | 1f60<br>0008<br>1f61<br>7763<br>7766<br>a040<br>a070<br>a0a0<br>a5c0<br>1f60 | 0004<br>0004<br>a600 |         | umulw2<br>addw2<br>movw<br>cmph<br>bne<br>andh2<br>br<br>orh2<br>xorh2<br>cmpb<br>be<br>movh<br>movb<br>movb<br>movb<br>movb<br>movb<br>movb<br>movk<br>movw<br>movw<br>movw<br>movw<br>movw<br>movw<br>movw<br>movw | &0x54,%r0<br>&0x0414c,%r0<br>%r0,%r8<br>\$0x41f6,&0x0<br>+0x6 <197a><br>&0x7fff,\$0x4594<br>+0x5 <1984><br>&-0x8000,\$0x4594<br>&0x1,\$0x41f6<br>\$0x4776,&0x3<br>+0x46 <1a1e><br>\$0x4776,&0x6<br>+0x42 <1a1e><br>&0x522,0x4(%fp)<br>&0x5c,0x7(%fp)<br>&0x5c,0x7(%fp)<br>&0x5c,0x8(%fp)<br>%r8,%r0<br>0x4e(%r0),0xa(%fp)<br>%r8,%r0<br>0x4e(%r0),0x5c(%fp)<br>\$0x41f6,0x60(%fp)<br>&0x0,%r7<br>+0x11 <19ee><br>%r7,%r0<br>&0x2,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r7,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r7,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r8,%r0<br>%r7,%r0<br>%r8,%r0<br>%r7,%r0<br>%r8,%r0<br>%r7,%r0<br>%r8,%r0<br>%r7,%r0<br>%r8,%r0<br>%r7,%r0<br>%r8,%r0<br>%r7,%r0<br>%r8,%r0<br>%r7,%r0<br>%r8,%r0<br>%r7,%r0<br>%r8,%r0<br>%r7,%r0<br>%r8,%r0<br>%r7,%r0<br>%r8,%r0<br>%r7,%r0<br>%r8,%r0<br>%r7,%r0<br>%r8,%r0<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1<br>%r2,%r1 |

|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                            | Nptcomp<br>andling f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -                                                                            | ol Fur               | nctions | 5ESS                                                                                                                                                                                                                 | PR-5D12010-71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                            | - 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | AM:INFPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MP IS                                                                        | SSUE (               | )1 P    | AGE 90<br>OVER PAG                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| AM:INFPUMP                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                              |                      |         |                                                                                                                                                                                                                      | 11/ 0/51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| [31]                                                                                                       | 19ea: 2a<br>19ee: 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | a61 0007                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                              |                      |         |                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |